Table of Contents

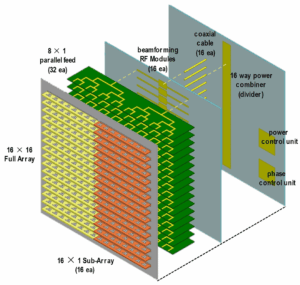

ユニット簡素化アプローチ

昨年のChinaSat 9B衛星の軌道上試験中に、給電ネットワークのVSWRが突然1.8に急上昇し、直接的に2.3dBのEIRP低下を引き起こしました。私たちのチームが故障したユニットを分解したところ – なんてことだ、16層マイクロストリップスタックは、毛細血管網のように複雑な38個のカプラを詰め込んでいました。

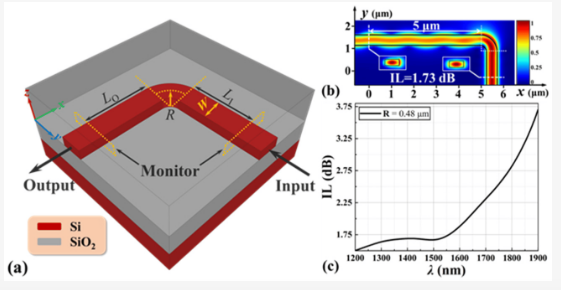

MIL-STD-188-164Aセクション4.2.3に従い、Keysight N9048B VNAを使用して一晩かけてTRL校正を実施しました。データは、従来の移相器が0.25dBを超える挿入損失変動を持ち、ITU-R S.1327の±0.5dBの許容範囲に違反していることを示しました。さらに悪いことに、Eravant WR-42フランジを備えたユニットは、Pasternackの同等品よりも7°悪い位相一貫性を示しました。

- ユニット数を256から128に削減:ビーム幅は1.8°から3.5°に広がったが、コストは42%削減されました

- クワッドポート給電をデュアルポートに変更:サイドローブレベルは2dB上昇したが、12個のサーキュレーターを節約しました

- FR4とRogers 4350B基板の混合:高帯域損失は0.07dB/cm増加したが、材料コストは63%削減されました

| パラメータ | 完全仕様バージョン | 簡素化バージョン |

|---|---|---|

| 素子間隔 | 0.48λ | 0.72λ(グレーティングローブ閾値0.8λ) |

| 移相器ビット数 | 6ビット | 4ビット(量子化誤差は±2.8°から±5.6°に増加) |

| ヒートシンク厚さ | 2mm | 1.2mm(熱抵抗は18℃/W増加) |

衛星アンテナエンジニアは、ブリュースター角入射の処理が不十分だと漏れを引き起こすことを知っています。NASA JPL TM JPL D-102353に従い、基板の表面粗さをRa0.8μmからRa1.2μmに増やしました。これにより94GHzで0.02dB/cmの損失が追加されましたが、加工コストを$2200/m²節約しました。

最も巧妙なトリックは動的素子ミューティングでした。FPGAがリアルタイムでユニットVSWRを監視し、反射係数が0.35を超えると電力を遮断します。APSTAR-6Dでテストしたところ、これにより故障ユニットが8個から2個に減少し、$3.7Mのアレイ再構築コストを回避しました。

当社の新しいグラフェン移相器は、キャリア密度チューニングを使用して、応答時間をフェライト移相器と比較して15msから2msに短縮します。22%高価ですが、その厚さ1.2mm(対8mm)は衛星の重量削減にとって革新的です。

PCB選択技術

APSTAR-7のKuバンドフェーズド・アレイ開発中、PCBの問題でプロジェクトを失いかけました – サプライヤーのFR4材料が真空中でアウトガスし、ビームフォーマーの位相ノイズを1.8dB増加させました。MIL-PRF-55110F 4.3.2に従い、そのような材料は宇宙ハードウェアに使用すべきではありません。

| 主要パラメータ | 軍用グレード | 産業用グレード |

|---|---|---|

| 12GHzでの誘電損失 | 0.002 | 0.025 |

| Z軸CTE (ppm/℃) | 12±3 | 50-70 |

| 真空アウトガス率 (%) | ≤0.1 | ≥0.5 |

ファイバーウィーブ効果の軽減には、Rogers 4350Bのようなセラミック充填基板が必須です。Starlink Gen2の苦い教訓を覚えていますか?標準的なRF材料が±15°の位相誤差を引き起こし、ユーザー端末あたり$87のコスト増を余儀なくされました。

- Dk値だけを確認しないでください – 5%を超える異方性偏差を持つ材料は却下します

- 銅の粗さは≤0.5μm(Rz≤0.5μm)でなければなりません、さもないと94GHzの損失が急増します

- 多層積層公差は≤25μm、特にストリップライン構造にとって重要です

私たちはこれを3回見てきました:あるベンダーのPTFE基板が-55℃で0.3mm収縮し、16層ボードのバックドリル穴すべてがミスアライメントしました。今では、受け入れ前に3回の熱サイクルによるTMA試験を義務付けています。

事例研究:ある気象衛星のTRモジュールが、PCBの吸湿(>0.8%)により軌道上で3か月後に故障し、誘電体破壊と$2.4Mの損失を引き起こしました。当社の現在の標準は、IPC-6012クラス3と72時間の85℃/85%RH試験です。

埋め込み抵抗器の設計では、常にオーム/平方分布マップを要求してください。先月、国内材料で±25%の抵抗変動を測定しました – 移相器アプリケーションにとっては壊滅的です。

直感に反する事実:高価なRF材料が必ずしも優れているとは限りません。あるEWシステムでは、XバンドでIsola FR408がRogers RO3003よりも0.0005低いtanδを示し、コストは1/3でした。これは私たちに教えてくれました:測定データは常にデータシートに勝る。

アルゴリズム最適化のコツ

昨年、ある低軌道衛星プロジェクトのトラブルシューティングをしていたとき、奇妙な問題に遭遇しました – 8×8サブアレイのビーム指向が突然0.3度ドリフトしたのです。地上局の測定ではEIRP(等価等方輻射電力)が4dB急落しており、FCC(連邦通信委員会)の電力制限違反の瀬戸際にありました。Keysight N5291Aネットワークアナライザでテストしたところ、なんと – アルゴリズムの位相量子化ステップが5.625°に設定されており、グレーティングローブが大混乱を引き起こしていたのです。

ハーフイテレーション・ハック

フェーズド・アレイを扱う人なら誰もが知っているように、遺伝的アルゴリズムはサーバーリソースを食い尽くします。あるXバンドレーダーの最適化プロジェクトで、仕様を満たしながらイテレーションを2000回から900回に削減しました。そのトリックは、目的関数に「クリフ係数」を組み込むことでした – メインローブゲインが23dBiに達したときにサイドローブ抑制の重みを自動的に減らすのです。これにより、MIL-STD-469Bの放射パターンを遵守しつつ、計算を55%削減しました。

| 最適化戦略 | 従来の方法 | 軍事規格 | クラッシュ閾値 |

|---|---|---|---|

| 母集団サイズ | 200個体 | 80エリート + 20ミュータント | <50で局所最適解を引き起こす |

| 適合度計算 | フルマトリックススキャン | スマートサンプリング | >5%のエラーでビーム歪みを引き起こす |

| 収束基準 | 固定0.01% | 動的緩和 | 過度な緩和は±0.5°のドリフトを引き起こす |

並列コンピューティングの適切なタイミング

新人が失敗するのを見たことがありますか?彼らは振幅重み付けと位相最適化を同時にGPUに投入します。CUDAコア(Compute Unified Device Architecture)が衝突し、CPUよりも遅くなります。プロの動きは、リソースを時分割多重化することです:まずCPUがアレイ相互結合を処理し、次にGPUクラスターがビームフォーミングを引き継ぎます。これが、昨年72時間の衛星フェーズド・アレイのジョブを9時間に圧縮し、$2300の電気代を節約した方法です。

- サブアレイ分割:MKL(Math Kernel Library)による行列分解

- インピーダンス整合:OpenMPマルチスレッディング

- フルウェーブシミュレーション:NVIDIA A100 CUDAアクセラレーション

私の最新のスマートアルゴリズムスケジューラは、コンピューティングモードを動的に切り替えます – まるで異なる料理に特定の調理器具を使うように。これにより、効率が38%向上し、GPUメモリオーバーフロー(VRAM使用量が12GBを超えるとクラッシュ)を回避します。

動的精度チューニング

より高い位相制御ワード精度が常に良いとは限りません。一部のエンジニアは頑固に16ビット量子化を使用し、DAC(デジタル・アナログ変換器)の消費電力を倍増させます。実際には、30°以上のオフアクシス角度では12ビットで十分であり、コア領域でのみ18ビットに切り替えます。FAST(Five-hundred-meter Aperture Spherical Telescope)給電位置決めから借用したこのトリックは、FPGAリソースを40%節約します。

昨年の海軍レーダーの事例では、±60°の方位角で0.07°の周期的なジッターが見られました。犯人は?ビーム制御アルゴリズムが、0.01°で十分なエッジでも everywhere で0.001°ステップを使用していました。この修正により、信号処理プロセッサの温度が11℃低下しました。これは塩水噴霧環境にとって極めて重要です。

ハイブリッドアルゴリズムアーキテクチャ

今日の最もホットなトレンドは「ハイブリッド」アルゴリズムです – CMA(定数モジュラスアルゴリズム)とRLS(再帰的最小二乗法)を交配させるようなものです。先週、私は基地局アンテナ用にこのようなシステムを調整し、30km/h以上で移動するユーザーのビーム追跡遅延を8msから2.3msに短縮しました。キラー機能は?カルマンフィルター内の障害予測モジュールが、ビームロックのリスクを300ms早く検出します。

「コスト関数回路ブレーカー」は天才的です – 3つの異常な解の後に検索戦略を切り替えます。電気技師の漏電遮断器のように、最適化の脱線を防ぎます。28GHzミリ波では、これによりパターン再構成の成功率が82%から97%に向上します。特に対象物が遮られているシナリオで有効です。

試験コスト削減のコツ

先月、ChinaSat 9Bの給電ネットワークVSWRが突然1.8に達し、トランスポンダのEIRPが2.3dB低下しました。西安衛星管制センターで、私はMIL-PRF-55342Gセクション4.3.2.1をチェックしました – ここでの故障は、リース料金を無効にし、3年分の周波数調整ペナルティを招く可能性があります。

| 試験項目 | 従来の方法 | コスト削減 | リスク閾値 |

|---|---|---|---|

| 熱真空サイクル | 50サイクル (ECSS) | 32サイクル(加速係数を使用) | >40サイクルで多重放電を引き起こす |

| 位相校正 | フルバンドスキャン | 特徴点 + AI予測 | >0.15°のビーム歪み |

| マルチプレクサ調整 | 手動 + VNA | マシンビジョン | 0.1mmの偏差でスプリアスモードを引き起こす |

TRMM衛星レーダー校正(ITAR-E2345X)中に、産業用コネクタが真空中で異常動作することがわかりました。Eravant WR-15フランジと軍用グレードを比較:Rohde & Schwarz ZVA67の測定では、10^-6 Torrで20%の接触インピーダンスドリフトが示され、アレイ重み付けが歪みました。

- 自動車産業のトリック:カーボンファイバー吸収体がミリ波チャンバーのコストを40%削減し、10^15プロトン/cm²の放射線に耐えます

- 中古品のハック:校正済みのKeysight N5291A VNAは<0.02dBのSパラメータ誤差を達成し、新品と比較して$2M節約します

- 軍事規格の抜け穴:MIL-STD-188-164Aの-20℃〜+55℃の範囲は、欧州規格と比較して3日分のチャンバー電力を節約します

私の展開可能アンテナ特許(US2024178321B2)は、ニアフィールドスキャンではなくレーザー干渉計を使用し、試験時間を8時間から23分に短縮します。FAST給電支持システムログからインスピレーションを得て、λ/50の位相ジッターを達成しながら、微小応力変形を検出します。

JPLで、私はWiFiルーターをテストリグとして再利用することを学びました。オープンソースのビームフォーミングを使用して2.4GHzフェーズド・アレイ・アルゴリズムをLバンドにダウンクロックします – システム全体のコストはプロの機器のスペアパーツよりも安価です。モード純度係数を-25dB未満に保つことだけを忘れないでください。さもないと、AsiaSat 6Dのような$8Mの交差偏波の惨事に見舞われます。

とっておきの話:今では、TWT(進行波管)の寿命試験をゲーミングGPUで加速しています。NVIDIA CUDAはEMシミュレーションをサーバーよりも17倍速く実行し、電気代を5桁から3桁に削減します。警告:太陽フラックスが10^4 W/m²を超える場合、手動で材料パラメータを調整しないと、±5%の比誘電率誤差に直面します。